CONFIDENTIAL

#### TIA LA

#### TELEVISION INTERFACE ADAPTOR (MODEL 1A)

#### GENERAL DESCRIPTION

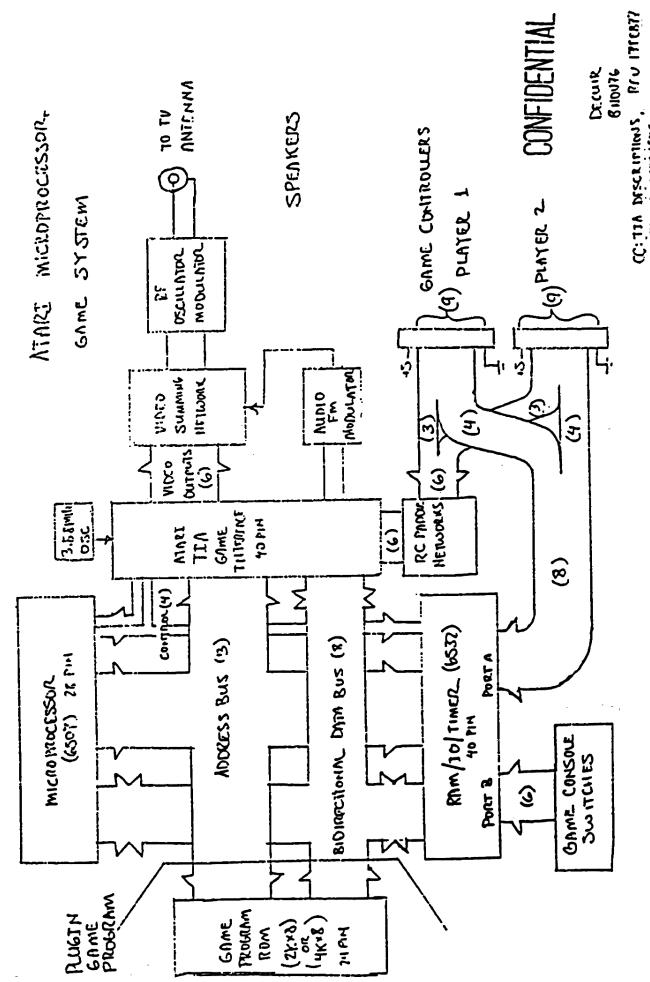

The TIALA is an MOS integrated circuit designed to interface between an eight (8) bit microprocessor and a television video modulator and to convert eight (8) bit parallel data into serial outputs for the color, luminosity, and composite sync required by a video modulator.

This circuit operates on a "line by line" basis, always outputing the same information every television line unless new data is written into it by the microprocessor.

A hardware sync counter produces horizontal sync timing independent of the microprocessor.

Vertical sync timing is supplied to this circuit by the microprocessor and combined into composite sync.

morizontal position counters are used to trigger the serial output of five (5) horizontally moveable objects; two players, two missiles, and a ball. The microprocessor can add or subtract from these position counters to move these objects right or left.

The microprocessor determines all vertical position and motion by writing zeros or ones into object registers before each appropriate horizontal line.

Walls, clouds and other seldom moved objects are produced by a low resolution data register called the playfield register.

A fifteen (15) bit collision register detects all fifteen possible two object collisions between these six (6) objects (five moveable and one playfield). This collision register can be read and reset by the microprocessor. Six input ports are also provided on this chip that can be read by the microprocessor. These input ports and the collision register are the only chip addresses that can be read by the microprocessor. All other addresses are WRITE only.

Color luminosity registers are included that can be programmed by the microprocessor with eight (8) luminosity and fifteen (15) color values. A digital phase shifter is included on this chip to provide a single color output with fifteen (15) phase angles.

Two (2) independent audio generating circuits are included, each with programmable frequency, noise content, and volume control registers.

#### DETAIL DESCRIPTION

#### 1. Data and addressing

Registers on this chip are addressed by the microprocessor as part of its overall RAM-ROM memory space.

The attached table of read-write addresses summarizes

the addressable functions. There are no registers

that are both read and write. Some addresses however are both read and write, with write data going

into one register and read data returning from a

different register.

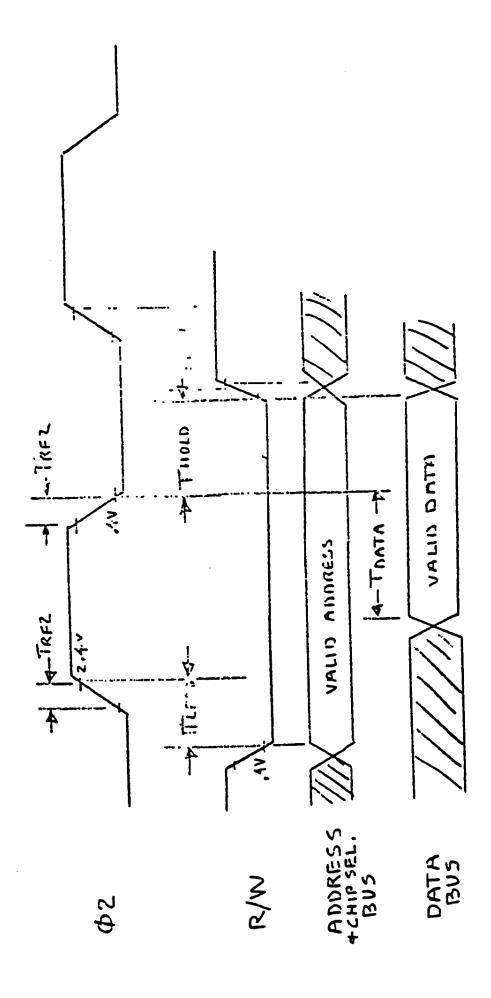

If the read-write line is low, the data bits indicated in this table will be written into the addressed write location when the 2 clock goes from high to low. Some registers are eight bits wide, some only one bit, an some (strobes) have no bits, performing only control functions (such as resets) when their address is written.

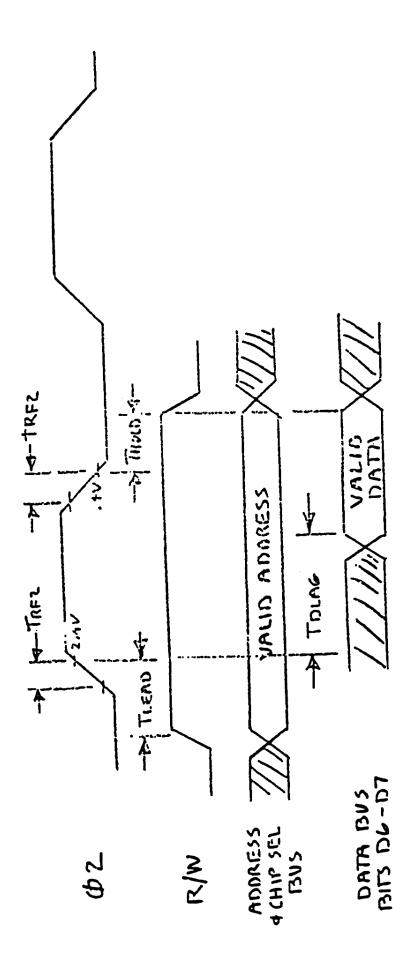

If the read-write line is high, the addressed location can be read by the microprocessor on data lines 6 and 7 while the 42 clock is high.

The addresses given in the table refer only to the six (6) real address lines. If any of the four (4) thip select lines are used for addressing, the addresses must be modified accordingly.

#### 2. Syncronization

## A. Horizontal Timing

A hardware counter on this chip produces all horizontal timing (such as sync, blank, burst) independent of the microprocessor. This counter is driven from an external 3.58 MHZ oscillator and has a total count of 228. Blank is decoded as 68 counts and sync and color burst as 16 counts.

### B. Vertical Timing

There are one bit, addressable registers on this chip for vertical sync and vertical blank. The timing for these functions is established by the microprocessor by writing zero or one into these bits. (VSYNC, V BLANK)

### C. Composite Sync

Horizontal sync and the output of the vertical sync bit are combined together to produce composite sync. This composite sync signal drives a chip output pad to an external composite video resistor network.

## D. Microprocessor Synchronization

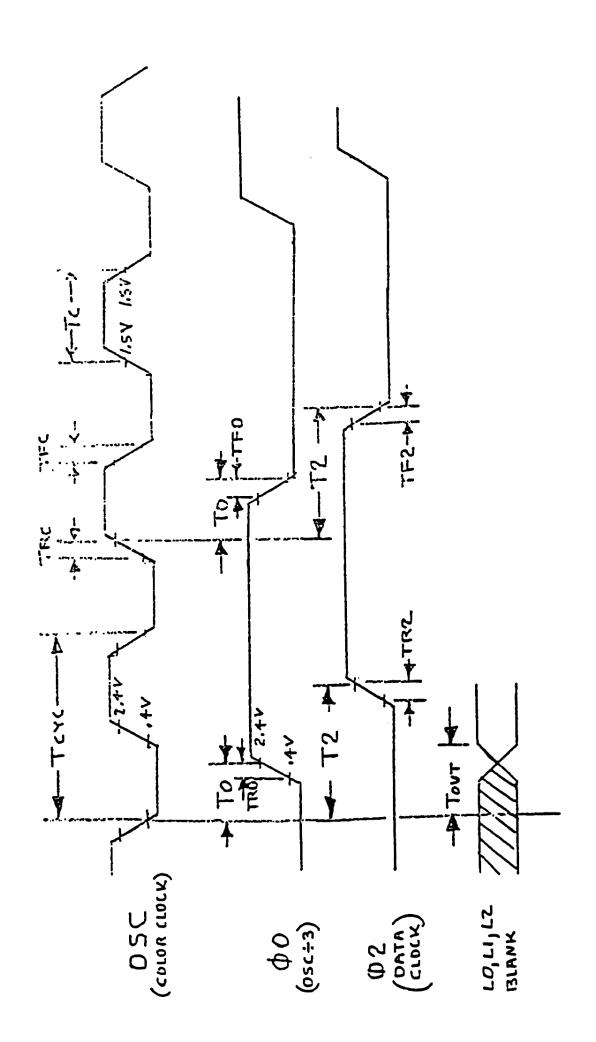

The 3.58 MHZ oscillator also clocks a divide by

three counter on this chip whose output (1.19 MHZ) is buffered to drive an output pad called \$0. This pad provides the input phase zero clock to the microprocessor which then produces the system \$\phi 2\$ clock (1.19 MHZ).

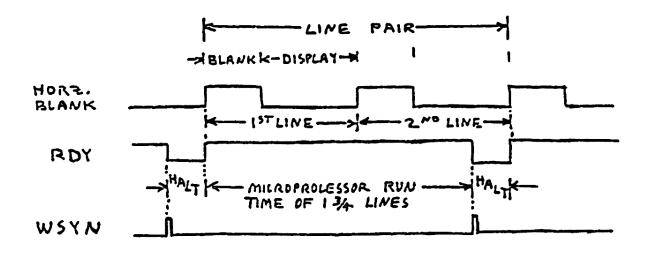

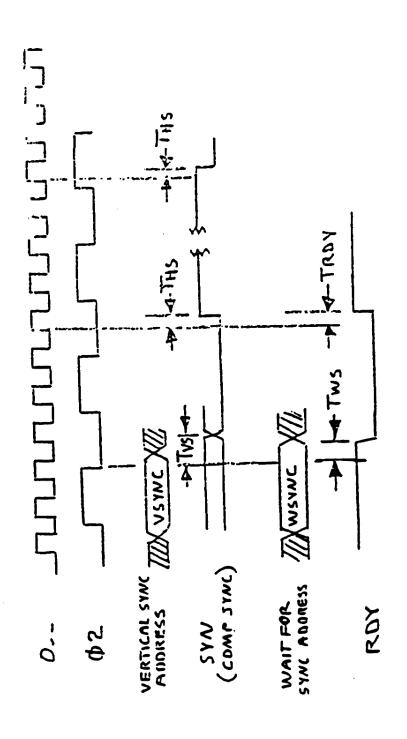

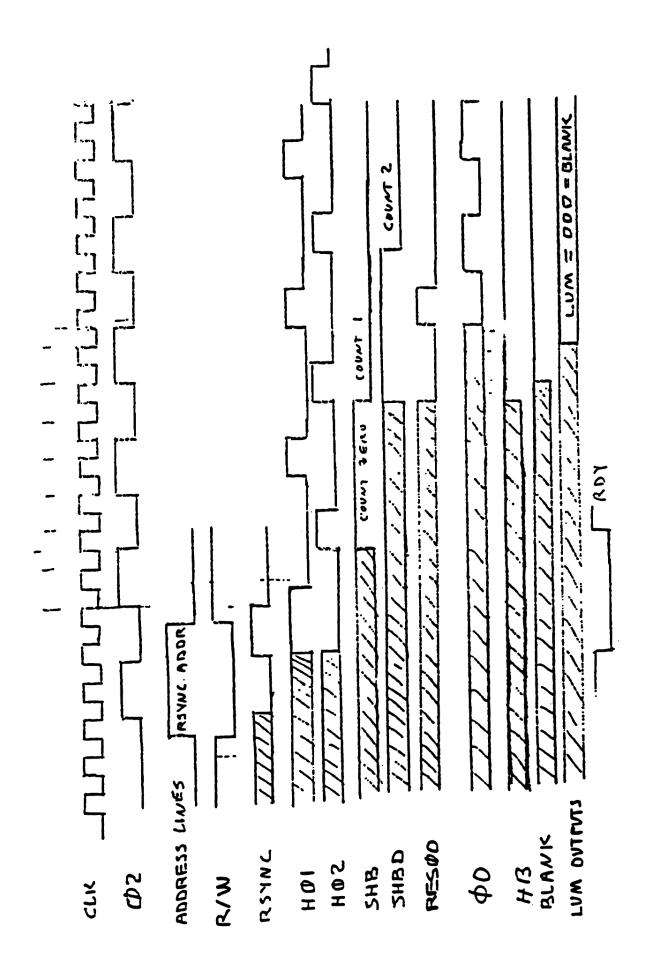

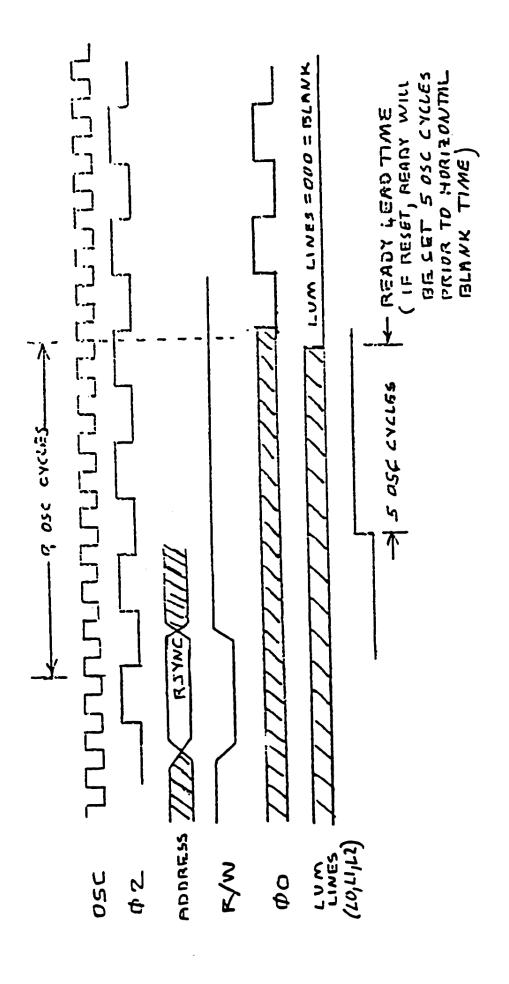

Software program loops require different lengths of time to run depending on branch decisions made within the program. Additional synchronization (Shown in Figure 2) is, therefore, required between the software and hardware. This is done with a one bit latch called WSYNC (wait for sync). When the microprocessor finishes a routine such as loading registers for a horizontal line, or computing new vertical locations during vertical blank, it can address WSYNC, setting this latch high. When this latch is high, it drives an output pad to zero connected to the microprocessor ready line (RDY). A zero on this line causes the microprocessor to halt and wait. As shown in figure 2, WSYNC latch is automatically reset to zero by the leading edge of the next horizontal blank timing signal, releasing the RDY line, allowing the microprocessor to begin its computation and register writing for this horizontal television line or line pair.

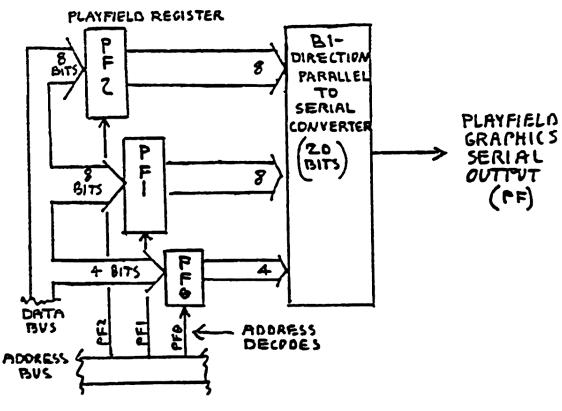

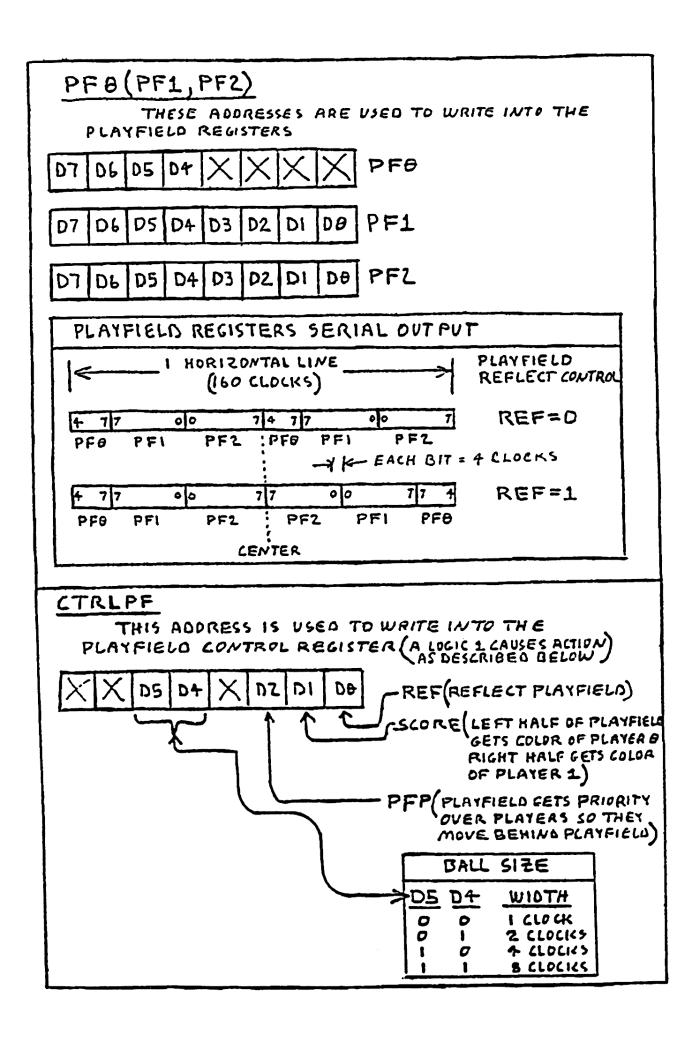

## 3. Playfield graphics Register

### A. Description

Objects, (such as walls, clouds, and score) which are not required to move, are written into a 20 bit register called the playfield register. This register (Figure 5) is loaded from the data bus by three separate write addresses (PFO, PF1, PF2). Playfield may be loaded at any time. To clear the playfield, zeros must be written into all three addresses.

## B. Normal Serial Output

The playfield register is automatically scanned (and converted to serial output) by a bi-directional shift register clocked at a rate which spreads the twenty (20) bits out over the left half of a horizontal line. This scanning is initiated by the end of horizontal blank (left edge of television screen). Normally the same scan is then repeated, duplicating the same twenty (20) bit sequence over the right half of the horizontal line.

## C. Reflected Serial. Output

A relected playfield may be requested by writing

a one into bit zero of the playfield control register (CTRLPF). When this bit is true the scanning shift register will scan the opposite direction during the right half of the horizontal line, reversing the twenty (20) bit sequence.

### D. Timing Constraints

Even though the playfield bytes (PFO, PF1, PF2) may be written at any time, if one of them is changed while being serially scanned, part of the new value may both show up on the television horizontal line.

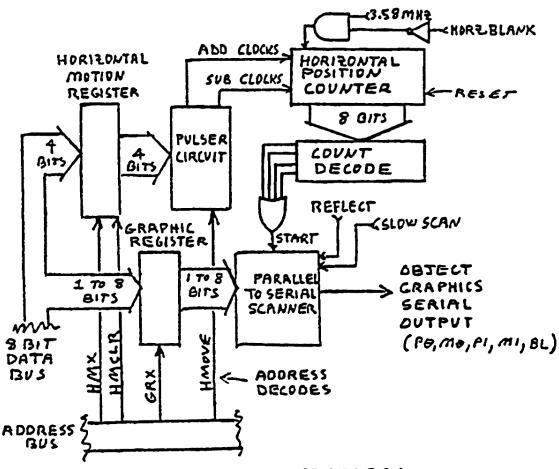

## 4. Eorizontal Position Counters

### A. Description

The playfield is a "fixed" graphics register, always starting its serial output when triggered by the beginning of each television line. This chip also includes five "moveable" graphics registers, whose serial outputs are triggered by five separate horizontal position counters every time these counters pass through zero count. These position counters are clocked continuously during the unblanke portion of every horizontal line and their count length is exactly equal to the normal number of clocks supplied to them during this time. They will therefore pass through zero at the same time du ing each horizontal television line and the triggered outputs will have no horizontal motion. A typical horizontal counter is shown in figure 4.

If extra clocks are supplied to these counters (or normal clocks suppressed) the zero crossing time will shift and he object will have moved left (extra clocks) or right (fewer Clocks). Some position counters have extra decodes (in addition to a zero decode) to trigger multiple copies of the same object across a horizontal line.

All position counters can be reset to zero count by the microprocessor at any time, by a write instruction to the reset addresses (RESBL, RESMO, RESM1, RESPO, RESP1). If reset occurs during horizontal blank, the object will appear at the left side of the television screen. Properly timed resets may position an object at any horizontal location consistent with the microprocessor cycle time.

## B: ...Ball Position Counter

The ball position counter has only the zero

crossing decode and therefore cannot trigger multiple copies of the ball graphics.

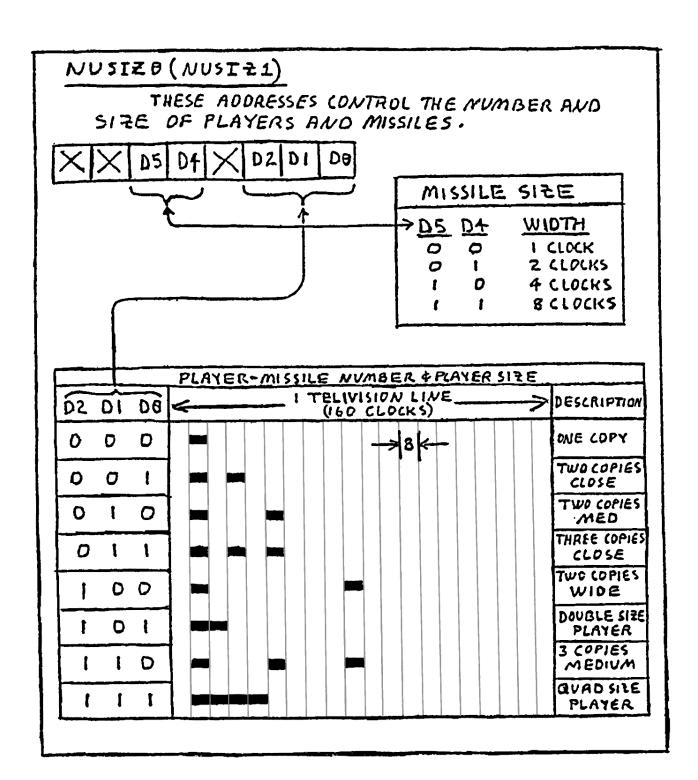

#### C. Player Position Counters

Each player position counter has three decodes in addition to the zero crossing decode. Those decodes are controlled by bits 0,1,2 of the number size control registers (NUSIZO, NUSIZI), and trigger 1,2, or 3 copies of the player (at various spacings) across a horizontal line as shown on page 20. These same control bits are used for the decodes on the missile position counter, insuring an equal number of players and missiles.

#### D. Missile Position Counters

Missile position counters are identical to player position counters except that they have another type of reset in addition to the previously discussed horizontal position reset. These extra reset addresses (RESMPO, RESMPI) write data bit 1 into a one bit register whose output is used to position the missile (horizontally) directly on top of its corresponding player, and to disable the missile serial output.

#### 5. Horizontal Motion Registers

### A. General Description

There are five write only registers on this chip that contain the horizontal motion values for each of the five moving objects. A typical horizontal motion register is shown in figure 4. The data bus (bits4 through7) is written into these addresses (HMPO, HMP1, HMMO, HMM1, HMBL) to load these registers with motion values. These registers supply extra (or fewer) clocks to the horizontal position counters only when commanded to do so by an HMOVE address from the microprocessor. These registers may all be cleared to zero (no mc.ion) simultaneously by an HMCLR command from the microprocessor, or individually by loading zeros into each register. These registers are each four bits in length and may be loaded with positive (left motion), negative (right motion) or zero (no motion) values. Negative values are represented in twos complement format.

#### D. Tiring Constraints

These registers may be loaded or cleared atalmost any time. The motion values they contain will be used only when an HMOVE command is addressed, and then all five motion values will be used simultaneously into all five horizontal position counters once. The only timing constraint on this operation involves the HMOVE command. The EMOVE command must be located in the microprocessor program immediately after a wait for sync (WSYNC) command. This insures that the EMOVE operation begins at the leading edge of homizontal blank, and has the full blank time to supply extra or fewer clocks to the horizontal position counters. These registers should not be modified for at least 24 Computer cycles after the

6. Hoving Object Graphics Registers EMove command.

#### A. General Description

There are five graphics registers for moving objects on this chip. These graphics registers are loaded (written) in parallel by the microprocessor and like the playfield register are scanned and converted to serial output. Unlike the playfield register, which is always scanned beginning at the left side of each horizontal line, moving object graphics registers are scanned only when triggered by a start decode from their horizontal position counter. A typical graphics register is shown in figure

## B. Missile Graphics

The graphics registers for both missiles are identical and very simple. They each consist of a one bit register called missile enable (ENAMO, ENAMI). This graphics bit is scanned (outputed) only when triggered by its corresponding position counter. There are control bits (bits 4,5, of NUSIZO, NUSIZI) that can stretch this single graphics bit out over widths of 1, 2, 4, or 8 clocks of horizontal line time. (A full line is 160 clocks).

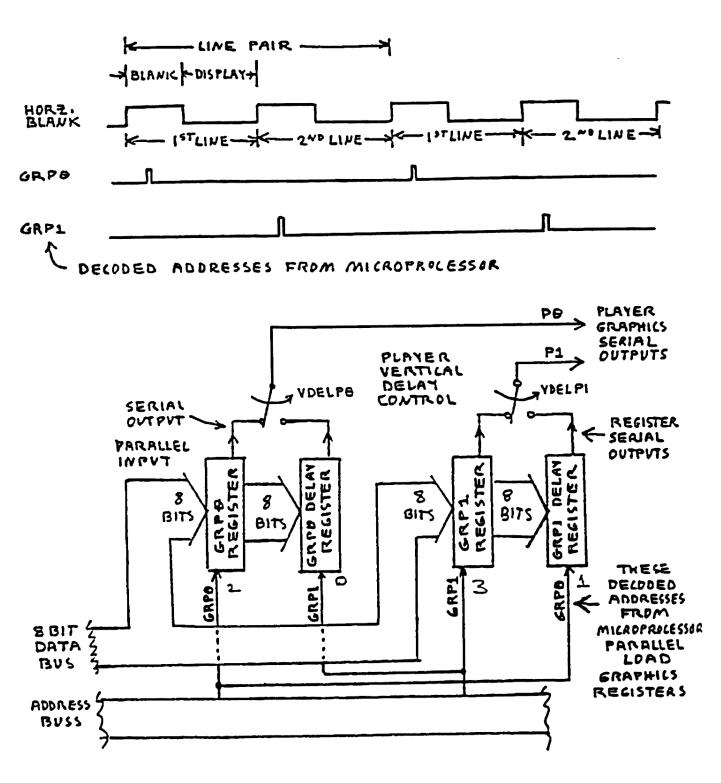

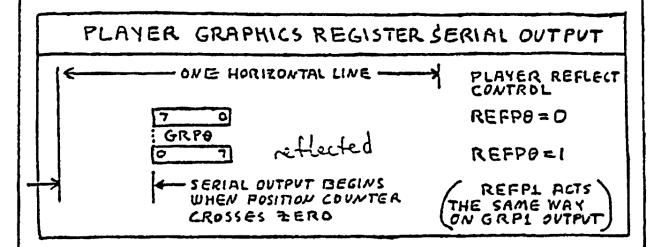

## C. Player Graphics

The graphics registers for both players are identical and are rather complex. They each consist of eight bit parallel registers (GRPO, GRP1) and a bi-directional parallel to serial

scan counter that converts the parallel data into serial output.

A one bit control register (REFPO, REFP1) determines the direction (reflection) of the parallel to serial scan, outputing either D7 through D0, or D0 through D7. This allows reflection (horizontal flipping) of player serial graphics data without having to flip the microprocessor data.

The clock into the scan counter can be controlled (three bits of NUSIZO and NUSIZI) to slow the scan rate and stretch the eight bits of serial graphics out over widths of 8, 16, or 32 clocks of horizontal line time. These same control bits are used in the playermissile motion counters to control multiple copies, so only three player widths (scan rates) are available.

### D. Vertical Delay,

Each of the player graphics registers actually consists of two 8 bit parallel registers. The first (GRPO, GRP1) is loaded (written) from the microprocessor 8 bit data bus. The second is automatically loaded from the output of the first. The reason for this is a complex subject called vertical delay. A large amount of microprocessor time is required to generate player, missile and playfield graphics (table look up, masking, comparisons, -ect.) and load these into this chip's registers. For most game programs this time is just too large to fit into one horizontal line time. In fact for most games it will barely fit into two line times (127 microseconds). Therefore, individual graphics registers are loaded (written) every two lines, and used twice for serial output between loads. This type of programming will obviously limit the vertical height resolution of objects to multiples of two lines. It also will limit the resolution of vertical motion to two lines jumps. Nothing can be done about the vertical height resolution; however, vertical motion can be resolved to a single line by addition of a second graphics register that is auto-

height resolution; however, vertical motion can be resolved to a single line by addition of a second graphics register that is automatically parallel loaded from the output of the first, one line time after the first was loaded from the data bus. This second graphics register output is therefore always delayed vertically by one line. A control bit called

of these two registers is to be used for serial output. If this control bit is set by the microprocessor between picture frames the object will be moved:down (delayed) by one line during the next frame. In most programming applications player 0 graphics and player 1 graphics are loaded (written) alternately, during the blank time just prior to each line as shown in (figure 1). Since GRPO and GRP1 addresses from the microprocessor alternate, they are delayed by one line from each other. The GRPO address decode can therefore be used to load the delayed graphics register for player 1, and GRP1 likewise to load the delayed graphics register for player 0. The two vertical delay bits (VDELO, VDEL1) then select delayed or undelayed registers for player 0 and player 1 as serial outputs.

vertical delay (VDELO, VDEL1) selects which

#### E. Ball Graphics

The ball graphics register is almost identical to the missile graphics register. It also consists of a single enable bit (ENABL) whose output is triggered by the ball position counter. It also has two control bits (bits 4, 5 of CTRLPF) that can stretch this single graphics bit out over widths of 1, 2, 4, or 8 clocks of horizontal line time. Unlike the missile graphics, however, the ball graphics register has capability for vertical delay similar to the player graphics. A second graphics (enable) bit is alternately loaded from the output of the first, one line after the first was loaded from the data bus. A ball vertical delay bit (VDELBL) selects which of these two graphics bits is used for the ball serial output. The first graphics bit (ENABL) should be loaded during the same horizontal blank time as player 0 (GRPO), because GRP1 is used to load the second enable bit from the output of the first on alternate lines.

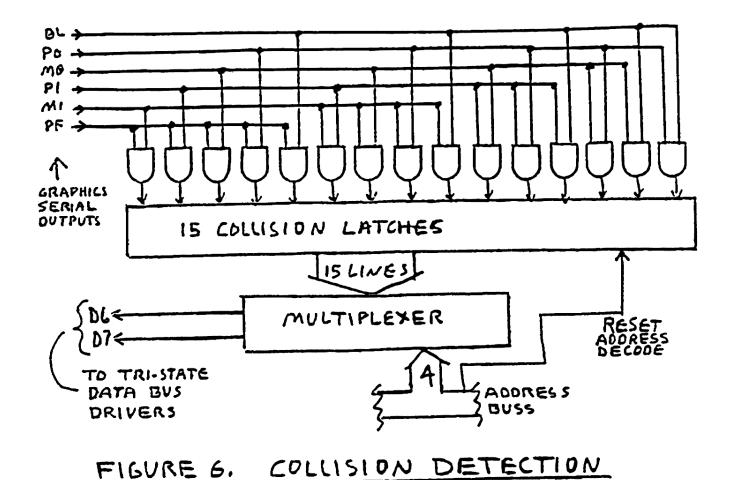

### 7. Collision Detection Latches

#### A. Definitions

The serial outputs from all the graphics registers represent real time horizontal location of objects on the television screen. If any of these outputs occur at the same time,

they will overlap (collide) on the screen. There are six objects generated on this chip (five moving and playfield allowing fifteen possible two object collisions. These overlaps (collisions) are detected by fifteen "and" gates whenever they occur, and are stored in fifteen individual latch register bits, as shown in figure 6.

#### E. Feading Collision

The microprocessor can read these fifteen collision bits on data lines 6 and 7 by addressing them two at a time. This could be done at any time but is usually done between frames (ouring vertical blank) after all possible collisions have serially occured.

#### C. Reset

All collision bits are reset simultaneously by the microprocessor using the reset address CXCLR. This is usually done near the end of vertical blank, after collisions have been tested.

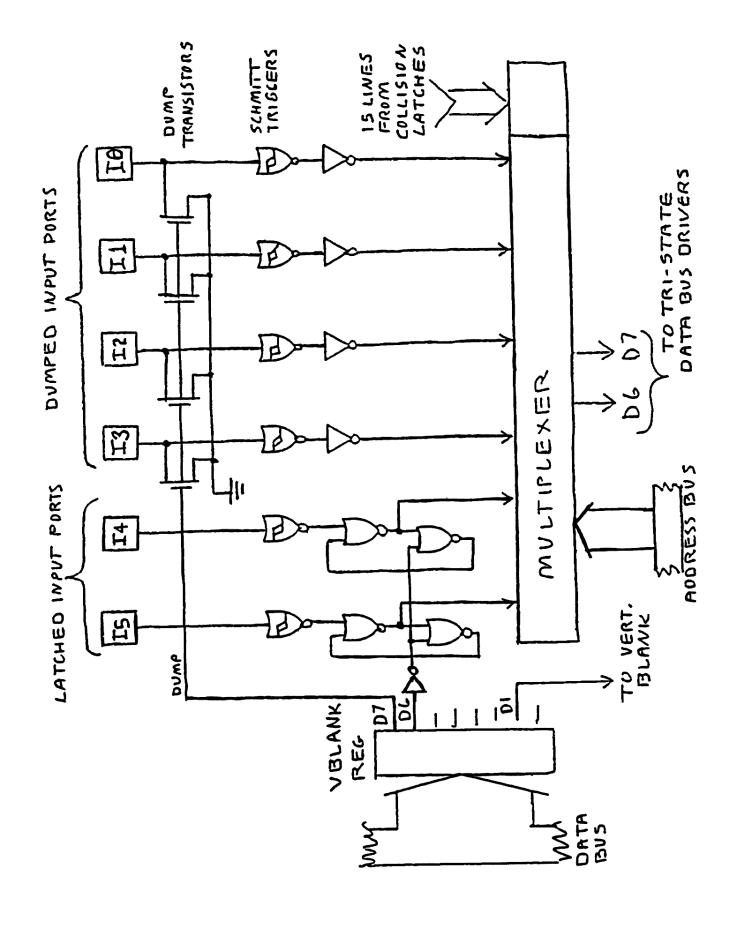

#### E. Input ports

#### A. General Description

There are 6 input ports on this chip whose logic state may be read on data line 7 with read addresses INPTO through INPTS. These 6 ports are divided into two types, "dumped" and "latched". See Figure 8.

## B. <u>Dumped Input Forts</u> (IO through I3)

These 4 input ports are normally used to read paddle position from an external potentiometer-capacitor circuit. In order to discharge these capacitors each of these input ports has a large transistor, which may be turned on grounding the input ports) by writing into bit 7 of the register VBLANK. When this control bit is cleared the potentimeters begin to recharge the capacitors and the microprocessor measures the time required to detect a logic 1 at each input port.

As long as bit 7 of register VBLANK is zero, these four ports are general purpose high inpedance input ports. When this bit is a 1 these ports are grounded.

## C. <u>Latched Input ports</u> (I4, I5)

These two input ports have latches which can be enabled or disabled by writing into bit 6 of register VBLANK.

When disabled, these latches are removed from the circuit completly and these ports become two general purpose input ports, whose present logic state can be read directly by the microprocessor.

When enabled, these latches will store negative zero logic level) signals appearing on these two input ports, and the input port addresses will read the latches instead of the input ports.

Latched Input Ports (I4, I5) - continued When first enabled these latches will remain positive as long as the input ports remain positive (logic one). A zero input port signal will clear a latch value to zero, where it will remain (even after the port returns positive) until disabled. Both latches may be simultaneously disabled by writing a zero into bit 6 of register VBLANK.

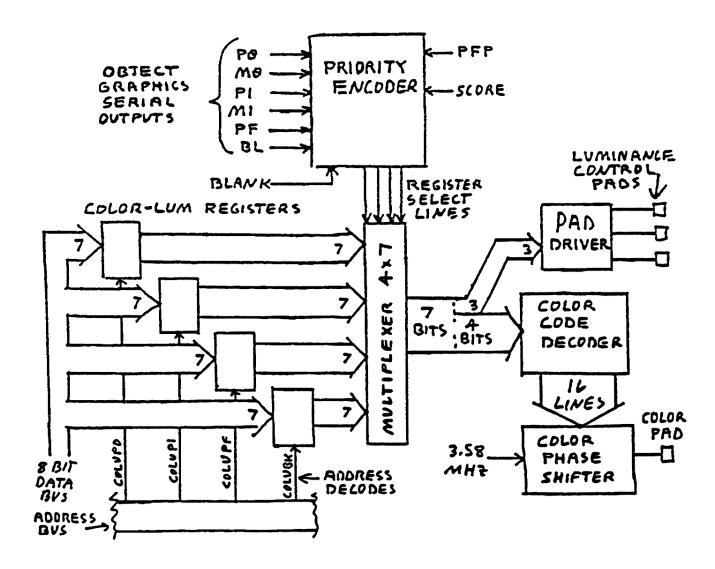

## E.S Priority Encoder

#### A. Purpose

As discussed in the section on collisions, simultaneous serial outputs from the graphics registers represent overlap on the television screen. In order to have color-luminosity values assigned to individual objects it is necessary to establish priorities between objects when overlapped. The priority encoder is shown in figure 3.

## B. Priority Assignment

The lack of any objects results in a color-lum value called the background. The background (BK) has lowest priority and only appears when no objects are outputing. In order to simplify the logic each missile is given the same color-lum value and priority as it's corresponding player (PO, MO) and the ball is given the same color-lum value and priority as the playfield (PF, BL).

The following table illustrates the normal priority assignment:

Righest Priority P0, M0

Second Righest P1, M1

Third Highest PF, BL

Lowest Priority BK

Objects with higher priority will appear to move in front of objects with lower priority. Players will therefore move in front of playfield (clouds, walls, etc.).

## C. Priority Control

There are two playfield control bits that affect priority, one called playfield priority(PFP) (bit 2 of CTRLPF) and one called score (bit 1 of CTRLPF). When a one is written into the PFP bit the priority assignment is modified as shown below.

Fighest Priority PF, BL

Second Highest P0, M0

Third Highest P1, M1

Lowest Priority BK

Players will then move behind playfield (clouds, wall, etc.).

When a one is written into the score control bit, the playfield is forced to take the color-lum of player 0 in the left half of the screen and player 1 in the right half of the screen. This is used when displaying score and identifies the score with the correct player.

The priority enco der produces 4 register select lines (shown in figure 3) that are mutually exclusive. These 4 lines select either background, player 0, player 1 or playfield, and only one of them can be true at a time.

## 9. Color Luminance Registers

#### A. Description

There are four registers (shown in figure 3) that contain color-lum codes. Four bits of color code and three bits of luminance code may be written into each of these registers (COLUPO, COLUPI, COLUPF, COLUBK) by the microprocessor at any time. These codes (representing 16 color values and 8 luminance values) are given in the Detailed Address List.

## B. Multiplexing

The serial graphics output from all six objects is examined by the priority encoder which activates one of the four select lines into a 4 X 7 multiplexer. This multiplexer (shown in figure 3) then selects one of the four color-lum registers as a 7 line output. Three of these lines are binary coded luminosity and go directly to chip output pads. The other four lines go to the color phase shifter.

## 10. Color Phase Shifter

This portion of the chip (shown in figure 3) produces a reference color output (color burst) during horizontal blank and then during the unblanked portion of the line it produces a color output shifted in phase with respect to the color burst. The The amount of phase shift determines the color and is selected by the four color code lines from the Color-lum multiplexer. Binary code 0 selects no color. Code 1 selects gold (same phase as color burst). Codes 2 (0010) through 15 (1111) shift the phase from zero through almost 360 degrees allowing selection of 15 total colors around the television color wheel.

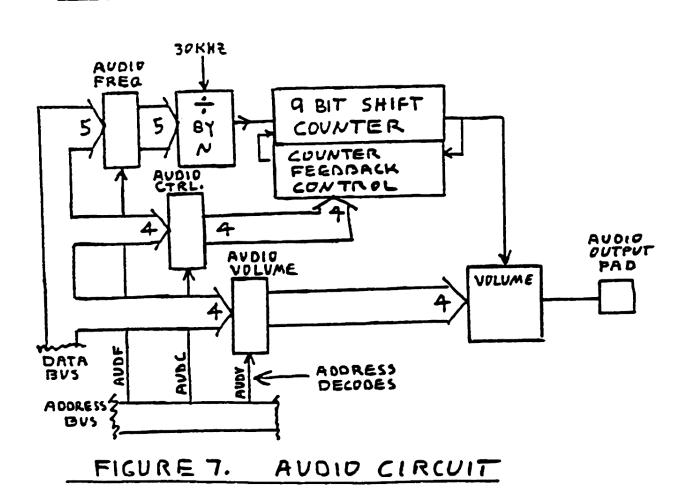

## 11. Av lio:Circuits

Two audio circuits are incorporated on this chip. They are identical and completely independent, although their outputs could be combined externally into one speaker. Each audio circuit consists of parts described below, and in figure 7.

#### A. Frequency Select

Clock pulses (at approximately 30 KHZ) from the horizontal sync counter pass through a "divide by N" circuit which is controlled by the output code from a five bit frequency register (AUDF). This register can be loaded (written) by the microprocessor at any time, and causes the 30 KHZ clocks to be divided by 1 (code 00000) through 32 (code 11111). This produces pulses that are digitally adjustable from approximately 30 KHZ to 1 KHZ and are used to clock the noise-tone generator.

#### B. Noise-Tone Generator

This circuit contains a nine bit shift counter which may be controlled by the ouput code from a four bit audio control register (AUDC), and is clocked by the frequency select circuit. The control register can be loaded by the microprocessor at any time, and selects different shift counter feedback taps and count lengths to produce a variety of noise and tone qualities.

### C. Volume Select

The shift counter ouput is used to drive the audio output pad through four driver transistors that are graduated in size. Each transistor is twice as large as the previous one and is enabled by one bit from the audio volume register (AUDV). This audio volume register may be loaded by the microprocessor at any time. As binary codes 0 through 15 are loaded, the pad drive transistors are enabled in a binary sequence. The shift counter output therefore can pull down on the audio ouput pad with 16 selectable impedance levels.

FIGURE 1 . VERTICAL DELAY

FIG. 2 SYNCRONIZATION

FIGURE 3. COLOR-LUMINANCE

FIGURE 4. HORIZONTAL MOTION CIRCUIT

FIGURE 5. PLAYFIELD GRAPHICS

FIGURE 8. INPUT PORTS

# WRITE ADDRESS DETAILED FUNCTIONS

WSYNC

wait for sync

THIS ADDRESS HALTS MICROPROCESSON BY CLEARING RDY LATCH TO ZERO. RDY 15 SET TRUE AGAIN BY THE LEADING EDGE OF HORIZONTAL BLANK.

DATA BITS NOT USED

RSYNC\_

24 Talga

THIS ADDRESS RESETS THE HORIZONTAL SYNC COUNTER TO DEFINE THE BEGINNING OF HORIZONTAL BLANK TIME, AND IS USED IN CHIP TESTING.

DATA BITS NOT VSED

VSYNC

THIS ADDRESS CONTROLS VERTICAL SYNC TIME BY WRITING DI INTO THE VSYNC LATCH.

NOT USED - .... DI ----

0

START VERT. SYNC

BLANK AND THE LATCHES AND DUMPING TRANSISTORS ON THE INPUT PORTS BY WRITING INTO BITS D7, DC AND D1 OF THE VBLANK REGISTER.

NOTE: DISSABLE LATCHES

(D6=0) ALSO RESETS

LATCHES TO LOGIC TRUE)

DISSABLE IA IS LATCHES

ODISSABLE IA IS LATCHES

LATCHES TO LOGIC TRUE

7 7 70

O REMOVE DUMP PATH TO GROUND

# RESPO (RESPI, RESMO, RESMI, RESBL)

THESE ADDRESSES ARE USED TO RESET PLAYERS

MISSILES AND THE BALL. THE DISTECT WILL BEGIN ITS

SERIAL GRAPHICS AT THAT TIME OF A HORIZONTAL LINE

AT WHICH THE RESET HODRESS OCCURS.

NO DATA BITS ARE USED

## RESMPO (RESMP1)

THESE ADDRESSES ARE USED TO RESET THE HORIZ.

LOLATION OF A MISSILE TO THE CENTER OF IT'S

CORRESPONDING PLAYER. AS LONG AS THIS CONTROL BIT

IS TRUE (1) THE MISSILE WILL REMAIN LOCKED TO THE

CENTER OF IT'S PLAYER AND THE MISSILE GRAPHICS

WILL BE DISSABLED, WHEN A ZERO IS WRITTEN INTO

THIS LOCATION THE MISSILE IS ENABLED, AND CAN

BE MOVED INDEPENDENTLY FROM THE PLAYER.

RESMP (MISSILE-PLAYER RESET)

## HMOVE

THIS ADDRESS CAUSES THE HORIZONTAL MOTION REGISTER VALUES TO BE ACTED UPON DURING THE HORIZONTAL BLANK TIME IN WHICH IT OCCURS. IT MUST OCCUR AT THE BEGINNING OF HORIZ. BLANK IN ORDER TO ALLOW TIME FOR GENERATION OF EXTRA CLOCK PULSES INTO THE HORIZONTAL POSITION COUNTERS. IF MOTION IS DESIRED, THIS COMMAND MUST IMMEDIATELY FOLLOW A WSYNC COMMAND IN THE PROCRAM.

NO DATA BITS ARE USED

## HMCLR

THIS ADDRESS CLEARS ALL HORIZONTAL MOTION REGISTERS TO ZERO (NO MOTION)

NO DATA BITS ARE USED

# HMPG(HMPI, HMMB, HMMI, HMBL)

THESE ADDRESSES WRITE DATA (HORIZONTAL MOTION VALUES) INTO THE HORIZONTAL MOTION REGISTERS. THESE REGISTERS WILL CAUSE HORIZONTAL MOTION DNLY WHEN COMMANDED TO DO SO BY THE HORIZ. MOVE COMMAND HMOVE.

THE MOTION VALUES ARE CODED AS SHOWN BELOW

| 07 | Db | D5 | D4 |     |                             |

|----|----|----|----|-----|-----------------------------|

| 0  | 1  | 1  | 1  | +7) |                             |

| ٥  | 1  | I  | 0  | +6  |                             |

| 0  | 1  | 0  | 1  | +5  | MOVE LEFT  INDICATED NUMBER |

| 0  | I  | 0  | D  | ++  | OF CLOCKS                   |

| 0  | 0  | Į. | 1  | 43  |                             |

| 0  | 0  | 1  | 0  | +2  |                             |

| D  | 0  | 0  | 1  | +1- | ,                           |

| 0  | O  | 0  | 0  | o_  | NO MOTION                   |

| 1  | 1  | t  | ŧ  | -1  |                             |

| i  | 1  | I  | 0  | -2  |                             |

| i  | 1  | D  | I  | -3  | MOVE RIGHT                  |

| 1  | I  | O  | 0  | -4  | > INDICATED NUMBER          |

| 1  | 0  | 1  | 1  | ~5  | OF CLOCKS                   |

| 1  | 0  | 1  | D  | -6  |                             |

| 1  | O  | O  | 1  | -7  |                             |

| 1  | Ø  | O  | 0  | -8/ | <i>)</i>                    |

WARNING: These motion registers should not be modified during the 24 Computer cycles immediately following an E Move command.

Unpredictable motion values may result.

# ENAMO (ENAM1, ENABL)

THESE ADDRESSES WRITE DI INTO THE I BIT MISSILE DR BALL GRAPHICS RECISTERS.

O DISSABLES OBJECT

I ENABLES OBJECT

## GRPB (GRP1)

THESE APPRESSES WRITE DATA INTO THE PLAYER GRAPHICS REGISTERS

D7 D6 D5 D4 D3 D2 D1 D0

## REFPO(REFPI)

THESE ADDRESSES WRITE D3 WTO THE 1 BIT PLAYER REFLECT REGISTERS.

O NO REFLECT (DT OF GRP ON LEFT)

REFLECT (DØ OF GRP ON LEFT)

## VDELPO (VDELPI, VDELBL)

THESE ADDRESSES WRITE DE INTO THE I BIT VERTICAL DELAY REGISTERS, TO DELAY PLAYERS OR BALL BY ONE VERTICAL LINE.

O NO DELAY

## CXCLR

THIS ADDRESS CLEARS ALL COLLISION LATCHES

TO ZERO (NO COLLISION)

DATA BITS NOT VSED

# COLUPB (COLUPI, COLUPF, COLUBK)

THESE ADDRESSES WRITE DATA INTO THE PLAYER, PLAYFIELD, AND BACKGROUND COLOR-LUMINENCE REGISTERS.

|                  |                | COLOR |    |    |    | LUM |    |     |            |

|------------------|----------------|-------|----|----|----|-----|----|-----|------------|

|                  |                |       |    |    |    |     |    |     |            |

|                  | COLOR          | D7    | Db | D5 | D4 | 03  | DS | DIX | LUM        |

| GP               | ley-gold       | 0     | 0  | 0  | 0  | 0   | 0  | 0   | BLACK      |

|                  | •              | 0     | 0  | D  | l  | 0   | 0  | 1   | dark grey  |

| 00               | ange , Red-Org | 0     | 0  | 1  | Q  | 0   | i  | 0   |            |

| UN               | ANGE MEDICINO  | 0     | 0  | ſ  | 1  | 0   | I  | 1   | GREY       |

| Pir              | NY = 0.100.0   | D     | 1  | 0  | ٥  | 1   | 0  | 0   | •          |

| 111              | PINK-PURPLE    |       | l  | 0  | 1  | 1   | 0  | •   | :          |

| PURP-BLUE BLUE   |                | 0     | 1  | 1  | 0  | 1   | 1  | 0   | LIGHT GREY |

| L M              | 1 Dear Dine    | 0     | 1  | 1  | 1  | 1   | ſ  | 1   | WHITE      |

| B                | ue - LT. Blue  | l     | ٥  | 0  | ٥  |     |    |     |            |

|                  | ar - Filippac  | i     | ٥  | 0  | Ī  | •   |    |     |            |

|                  | •              | ı     | 0  | 1  | 0  |     |    |     |            |

| TOAQ - GAN. BLUE |                | i     | ۵  | i  | i  | j   |    |     |            |

| GANYEL.,GAN      |                | 1     | 1  | D  | ٥  |     |    |     |            |

|                  |                | •     | •  | _  |    |     |    |     |            |

| _                |                | •     | 1  | 0  | -  |     |    |     |            |

| 06               | 16.6AN-LT.ORG. | 1     | 1  | ı  | 0  |     |    |     |            |

|                  | 1              | ì     | I  | ŧ  | l  | 1   |    |     |            |

## AVDF8 (AUDF1)

THESE ADDRESSES WRITE DATA INTO THE AUDIO FREQUENCY DIVIDER REGISTERS.

| D4  | 23         | DZ  | ומ    | DB  | 30KHS DIVIDED BY             |

|-----|------------|-----|-------|-----|------------------------------|

| 000 | 000        | 000 | 0 0 1 | 010 | DIVIDE BY 2 DIVIDE BY 3      |

| 1   | <br>1<br>1 | 1   | 1     | 0   | DIVIDE BY 31<br>DIVIDE BY 32 |

# AUDCB(AUDC1)

THESE ADDRESSES WRITE DATA INTO THE AUDIO CONTROL REGISTERS WHICH CONTROL THE NOISE CONTENT AND ADDITIONAL DIVISION OF THE AUDIO OUTPUT.

|               | D3       | DZ | DI | DВ | TYPE OF NOISE            |

|---------------|----------|----|----|----|--------------------------|

| HEX CODE      | <u> </u> |    |    |    | OR DIVISION              |

| 0             | 0        | 0  | 0  | 0  | SET TO 1                 |

| ι             | 0        | 0  | 0  | (  | 4 BIT POLY               |

| 2             | O        | 0  | 1  | 0  | ÷15→4BIT POLY            |

| 3             | 0        | 0  | 1  | l  | 5BITPOLY→4BIT POLY       |

| 4             | 0        | ı  | 0  | 0  | ÷2 } puretone            |

| 5             | 0        | 1  | 0  | ı  | • - \ 1                  |

| 6             | 0        | ſ  | 1  | 0  | ÷31 )                    |

| 7             | 0        | 1  | 1  | 1  | SBIT POLY → +2           |

| 8             | I        | 0  | 0  | 0  | 9 BIT POLY (WHITE NOISE) |

| q             | 1        | 0  | 0  | l  | 5 BIT POLY               |

| A             | 1        | 0  | 1  | 0  | ÷31 } pure tone          |

| B             | 1        | 0  | 1  | ŧ  | SET LAST 4 BITS TO 1     |

| C             | 1        | 1  | 0  | 0  | ÷6 7                     |

| $\mathcal{D}$ | 1        | 1  | 0  | 1  | +6 { fure to al          |

| ٤             | 1        | 1  | 1  | 0  | ÷93 )                    |

| F             | 1        | 1  | 1  | 1  | 5 BIT POLY ÷6            |

## AUDVO (AUDV1)

THESE ADDRESSES WRITE DATA INTO THE AUDIO VOLUME REGISTERS WHICH SET THE PULL DOWN IMPEDANCE DRIVING THE AUDIO OVTPUT PADS.

| <b>D3</b> | 02 | DI | DB | AUDID DUTPUT PULLDOWN CURRENT |

|-----------|----|----|----|-------------------------------|

| 0         | 0  | 0  | 0  | NO DUTPUT CURRENT             |

| 0         | D  | 0  | 1  | LOWEST                        |

| D         | 0  | 1  | D  |                               |

| -         | _  | -  | -  |                               |

| 1         | 1  | 1  | 0  |                               |

| ı         | 1  | 1  | 1  | HIGHEST                       |

## WRITE ADDRESS SUMMARY PE 1 OF 2

6 BIT DATA BITS ADDRESS ADDRESS FUNCTION こっにっ NAME 76543210 OCT HEX VERTICAL SYNC SET-CLEAR OOLOOL USYNC ١ VERTICAL BLANK SET-CLEAR VBLANKIII ı 01 01 WAIT FOR LEADING EDGE WSYNC 021 02 STRIOBE OF HORIZONTAL BLANK RESET HORIZONTAL STROBE 03 RSYNC 03 SYNC COUNTER NUMBER-SIZE 11 111 NUSIZB 04104 PLAYER-MISSILE & NUMBER - SIZE 05 05 NUSIZI 1 1 1 1 1 PLAYER-MISSILE 1 COLOR-LUM PLAYER & 1111 111 O61 COLUPO 06 COLUR - LUM PLAYER 1 1111111 COL UP1 07 07 COLOR-LUM PLAYFIELD 111 1 1 1 1 COLUPF 08 10 COLOR-LUM BACKGROUND 1111 (11COLUBK 09 11 CONTROL PLAYFIELD 11 111 CTRLPF 12 OAI BALL SIZE AND COLLISIONS REFLECT PLAYER O REFPO 1 13 OB REFLECT PLAYER 1 1 OC REFP1 14 PLAYFIELD REG. GYTE 1111 PFA 15 0D PLAY FIELD REG. BYTE 1111 1 1 1 1 OE PF1 16 PLAY FIELD REG. BYTE 2 1111 OF PFZ 1 1 1 1 1 17 RESET PLAYER O STROBE RESPO 20 10 RESET PLAYER 1 STRIDBE RESP1 21 11 STROBE RESET MISSILE & 22 12 RESMO STROBE RESET MISSILE 1 RESMI 23 13 RESET BALL RESBL STRIDBE 24 14 AUDID CONTROL & 1111 25 15 ANDCO AUDIO CONTROL 1 1111 AVDC1 26 16

REV. 1976

# WRITE ADDRESS SUMMARY F62 OF 2

| WINITE TIPONESS SOMMITTING |     |                 |         |         |                             |  |  |

|----------------------------|-----|-----------------|---------|---------|-----------------------------|--|--|

| 6 B<br>ADDR                |     | ADDRESS<br>NAME | DATA I  |         | FUNCTION                    |  |  |

| OCT                        | HEX | 707(11.12       | 7654    | 3210    |                             |  |  |

| 27                         | 17  | AUDFO           | 1       | 1111    | AUDID FREQUENCY 9           |  |  |

| 30                         | 18  | AUDF1           | 1       | 1111    | AUDIO FREGUENCY 1           |  |  |

| 31                         | 19  | AUDVG           |         | 1111    | AVDID VOLUME &              |  |  |

| 32                         | IA  | AUDV1           |         | 1111    | AUDIO VOLUME 1              |  |  |

| 33                         | IB  | GRPO            | 1111    | 1111    | GRAPHICS PLAYER 8           |  |  |

| 34                         | 10  | GRP1            | 1111    | 1 ] 1 i | GRAPHICS PLAYER 1           |  |  |

| 35                         | 10  | ENAMO           |         | i       | GRAPHICS (ENABLE) MISSILE & |  |  |

| 36                         | IE  | ENAM1           |         | 1       | GRAPHICS (ENABLE) MISSILE 1 |  |  |

| 37                         | 15  | ENABL           |         | 1       | GRAPHICS (ENABLE) BALL      |  |  |

| 40                         | 20  | НМРӨ            | 1111    |         | HOR ZUNTAL MOTION PLAYER &  |  |  |

| 41                         | 21  | HMP1            | 1111    |         | HORIZONTAL MOTION PLAYER 1  |  |  |

| 42                         | 22  | HMMB            | 1131    |         | HORIZONTAL MOTTON MISSILE & |  |  |

| 43                         | 23  | HMM1            | 1 1 4 1 |         | HURIZUNTAL MOTTON MISSILE 1 |  |  |

| 44                         | 24  | HMBL            | 1111    |         | HORIZONTAL MOTION BALL      |  |  |

| 45                         | 25  | VDELPO          |         | 1       | YERTICAL DELAY PLAYER P     |  |  |

| 46                         | 26  | VDELP1          |         | 1       | VERTICAL DELAY PLAYER 1     |  |  |

| 47                         | 27  | VDELBL          |         | 1       | VERTICAL DELAY BALL         |  |  |

| 50                         | 28  | RESMPO          |         | ١       | RESET MISSILE O TO PLATER O |  |  |

| 51                         | 29  | RESMP1          |         | . 1     | RESET MISSILE 1 TO PLAYER 1 |  |  |

| 52                         | 2A  | HMOVE           | STI     | ROBE    | APPLY HORIZONTAL MOTION     |  |  |

| 53                         | ZB  | HMCLR           | 5TR     | OBE     | CLEAR HORIZ, MOTION REGS.   |  |  |

| 54                         | 50  | CXCLR           | STR     | DBE     | CLEAR COLLISION LATCHES     |  |  |

|                            |     |                 |         |         |                             |  |  |

|                            |     |                 |         |         |                             |  |  |

# READ ADDRESS SUMMARY PE I OF I

|          |              | KEH    | U /113 | U 17 L. | 3 30/1///////  |            |          | ١_         |

|----------|--------------|--------|--------|---------|----------------|------------|----------|------------|

|          | ADDRESS NAME |        |        | ED      | FUNCTI         | ON         |          | REV<br>NOV |

| OCT      | HEX          |        | 7654   | 3210    |                | D7         | D6       | 1976       |

| 00       | ٥٥           | CXMBP  | 1 1    |         | READ COLLISION | MB.PI      | Mø, Pe   |            |

| 01       | 01           | CXMIP  | 1 1    |         | ıt             | MIPE       | MI·PI    |            |

| 02       | 02           | CXPOFB | 11     |         | 11             | POPF       | P0.BL    |            |

| 03       | 03           | CXPIFB | 1 1    |         | 11             | PIPF       | PIBL     |            |

| 04       | 04           | CXMOFB | 1 [    |         |                | Merpe      | WOIBL    |            |

| 05       | 05           | LXMIFB | 11     |         |                | MIPF       | WI .BL   |            |

| 06       | 06           | CXBLPF | 1      |         |                | BL.PF      | JUSE D   |            |

| 07       | 07           | CXPPMM | 1 1    |         |                | POPI       | MO·MI    | 1          |

| 10       | 08           | INPTO  | 1      |         | READ POT PORT  | Ie         |          |            |

| 11       | 09           | INPTI  | 1      |         | READ POT PORT  | II         | \ /      | _          |

| 12       | OA           | INPT2  | ١      |         | READ POT PORT  | 12         | \ /      | 1          |

| 13       | OB           | INPT 3 | 1      |         | READ POT POR   | T3         | //       |            |

| 14       | OC           | INPT 4 | 1      |         | READ INPUT     | I4         | / \      | 4          |

| 15       | ao           | Z TANE | 1      |         | READ IMPUT     | <b>I</b> 5 | /        | 4          |

|          |              |        |        |         | NOTE . IE      | ; I1, I    | 2,13     |            |

|          | 1            |        |        |         |                |            |          |            |

| -        | +-           |        |        | -       | SCFT WARE      | ONTROL     |          |            |

| <u> </u> |              |        |        |         | I4, I5 CAN     | be CON     | reated t |            |

| 1        |              |        |        |         | LATCHED IMP    | DAN 2TU    | ker      |            |

|          | +            | +      |        |         | SOFTWARE C     | ONTROL     | •        |            |

|          |              |        |        |         |                |            |          |            |

| -        | +-           | -      |        |         |                |            |          |            |

| -        | $\dashv$     |        |        |         |                |            |          |            |

| -        | +-           |        |        |         |                |            |          |            |

|          |              |        |        |         |                |            |          |            |

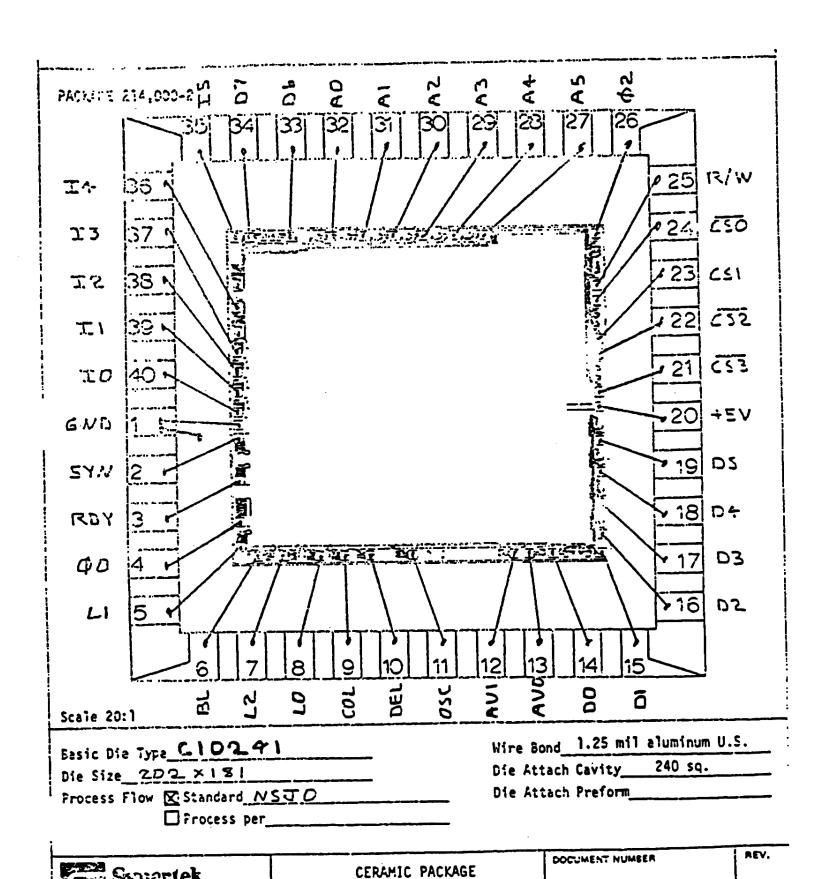

BONDING DIAGRAM

SHEET

| CHARACTERISTIC         | SYMBOL  | MIN  | TYP | MAX | UNIT         |

|------------------------|---------|------|-----|-----|--------------|

| GSC CYLLE TIME         | TCYC    | 2.60 | 280 |     | NSEC         |

| OSC DUTY CYCLE         | TC/TCYC | -45  | 50  | 55  | PERLEY       |

| OSC RISE-FAIL TIMES    | TRC-TEC |      |     | 2.5 | NSEC         |

| 40 (OSC+3) DELAY       | To      |      |     | 100 | NSEC         |

| on rise-fail tunes     | TRO-TEO |      |     | 25  | NSEC         |

| OR ( DATA CLOCK) DELAY | T2      |      |     | 250 | NSEC         |

| LUMINANCE DELAY        | Tout    |      |     | 100 |              |

| TOME SWAC DELAY        | Tys     |      |     |     | NSEC         |

| HORIT SYNC DELAY       | THS     |      |     | 100 | NSEC<br>NSEC |

| WAIT FOR SYME DELAY    | Tws     |      |     | 100 | NSEC         |

| PORDY DELAY            | TROY    |      |     | 100 | NSEC         |

| SMIT CADS COA-WAR      | TLEAD   | 180  |     |     | NSEC         |

| CATA BUS LEAD TIME     | · ·     | 300  |     |     | NSEC         |

| באיד שופא הדאמ-פקה     | THOLD   | 10   | İ   | ļ   | NSEC         |

| OZ RISE-FA TIME        | TRES    |      |     | 25  | NSEC         |

| BWLL SAT KLAD GETTI    | TOLAG   |      | İ   | 395 | NSEC         |

|                        |         | ĺ    |     | į   |              |

|                        |         | •    |     | İ   |              |

|                        |         |      | ł   | 1   |              |

|                        |         |      |     |     |              |

|                        |         |      |     |     |              |

|                        |         | İ    |     |     |              |

|                        |         | 1    |     |     |              |

|                        |         |      |     | 1   |              |

|                        |         |      | 1   | j   |              |

|                        |         |      | 1   |     |              |

|                        | 1       | 1    | 1   |     |              |

|                        |         |      | ı   |     |              |

|                        | ĺ       |      | 1   | 1   |              |

|                        |         | 1    |     | 1   |              |

|                        | İ       |      | 1   | 1   |              |

|                        |         |      |     |     |              |

TIA TIMING CHARACTERISTICS

TIA GO- GZ AND LUM TIMING

TEN WILLE TIMING CHATACTERISTICS

READ TIMING CHARACTERISTICS とエト

**JAIMI** TIR COMP-SYN AND READY

上がしるの RSYNC AND BLANK AND READY せ ト

CC: TIA DISCRIFITANS, FAIRM FINE AND MITS

## SARA PROGRAMMING INSTRUCTIONS

Sara is a 128 by 8 RAM that is Memory mapped into the VCS cartridge slot (F000 to FFFF). RAM write addresses are F000 to F07F. RAM read addresses are F080 to F0FF. The RAM read and write adresses over ride the ROM in that address space. Sara RAM cannot be used as program space i.e., data storage only.

Accessing Sara can be done by most instructions with address modes: absolute, absolute indexed by X, absolute indexed by Y, indexed indirect, or indirect indexed by Y. The exceptions are any instruction that required the 6507 to read RAM, modify the data, and write that data back into memory. Also in the indexing modes, the address plus the index cannot cross a page boundry, where a page boundry size is 256 bytes.

#### VCS CARTRIDGE MEMORY MAP

| FFFF         | ROM       |

|--------------|-----------|

| FOFF<br>FO80 | RAM Read  |

| F07F<br>F000 | RAM Write |